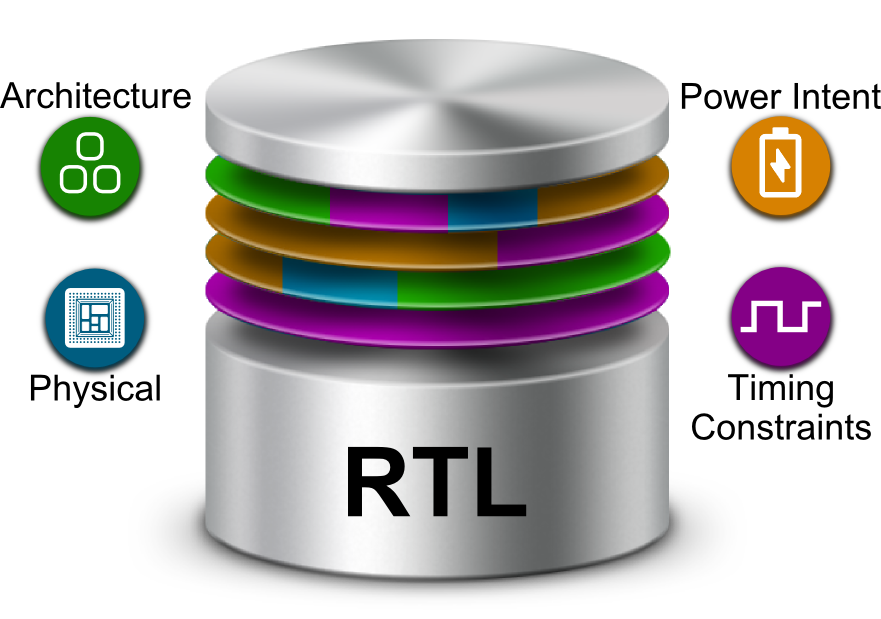

DISEÑO RTL

Un diseño a nivel funcional o de comportamiento (behavioral description) permite describir circuitos digitales atendiendo únicamente a las relaciones existentes entre las entradas y salidas del circuito, pero sin hacer referencia a la estructura real o hardware del que se compone el circuito. Existen dos tipos de descripciones a nivel de comportamiento en Verilog:

• Descripción RTL (r egister transfer level ): Es un nivel de abstracción mayor que el diseño estructural. Trabaja sobre variables tipo net, es decir, para implementar lógica combinacional. Utiliza la “asignación continua” (assign continuous assignment) para crear las relaciones lógicas existentes entre las entradas y las salidas. Esta descripción es siempre sintetizable, es decir, los programas de síntesis permiten crear los esquemáticos equivalente

. • Descripción basada en algoritmos: Este nivel de abstracción es mayor que el RTL. Trabaja sobre variables de tipo “reg”. Puede ser utilizado para describir circuitos combinacionales y circuitos secuenciales. Utiliza principalmente las construcciones “initial” y “always” como veremos más adelante. Ejecuta instrucciones de control de flujo comunes a muchos lenguajes de programación de alto nivel. Esta descripción no siempre es sintetizable, aún cuando se pueda simular el comportamiento especificado sin ningún problema.

Comentarios

Publicar un comentario